# Concurrent library correctness on the TSO memory model

Sebastian Burckhardt<sup>1</sup>, Alexey Gotsman<sup>2</sup>, Madanlal Musuvathi<sup>1</sup>, and Hongseok Yang<sup>3</sup>

<sup>1</sup> Microsoft Research

<sup>2</sup> IMDEA Software Institute

<sup>3</sup> University of Oxford

**Abstract.** Linearizability is a commonly accepted notion of correctness for libraries of concurrent algorithms. Unfortunately, it is only appropriate for sequentially consistent memory models, while the hardware and software platforms that algorithms run on provide weaker consistency guarantees. In this paper, we present the first definition of linearizability on a weak memory model, Total Store Order (TSO), implemented by x86 processors. We establish that our definition is a correct one in the following sense: while proving a property of a client of a concurrent library, we can soundly replace the library by its abstract implementation related to the original one by our generalisation of linearizability. This allows abstracting from the details of the library implementation while reasoning about the client. We have developed a tool for systematically testing concurrent libraries against our definition and applied it to several challenging algorithms.

#### 1 Introduction

Concurrent software developers nowadays rely heavily on libraries of concurrency patterns and high-performance concurrent data structures, such as java.util.concurrent for Java and Intel's Threading Building Blocks for C++. The algorithms implemented by these libraries are very efficient, with the downside being that they are notoriously difficult to design and implement. More surprisingly, it is often difficult to understand even what it means for them to be correct! Correctness of concurrent libraries is commonly formalised by the notion of *linearizability* [10], which fixes a certain correspondence between the library and its abstract specification, the latter usually sequential, with methods implemented atomically. Unfortunately, the classical definition of linearizability is only appropriate for sequentially consistent (SC) memory models, in which accesses to shared memory occur in a global-time linear order. At the same time, most multiprocessors (x86 [14], Power [16], ARM [1]) and programming languages (Java [11], C++ [2]) provide weaker memory models that allow more efficient implementations at the expense of exhibiting counterintuitive behaviours in some cases.

In this paper, we present the first definition of linearizability on a weak memory model, Total Store Order (TSO), implemented by x86 processors [14] (Section 4). We show that our definition is a correct one in the sense that it validates what we call the Abstraction Theorem: while proving a property of a client of a concurrent library, we can soundly replace the library by its abstract implementation related to the original one by

our generalisation of linearizability (Theorem 4, Section 5). The abstract implementation is usually simpler than the original one, with commands executing at a coarser grain of atomicity. The Abstraction Theorem thus formalises the intuitive requirement for a good definition of linearizability, which is that the library should provide an illusion of such a simpler atomic implementation. It also has a practical value as a compositional verification technique: it allows abstracting from the details of the library implementation while reasoning about its client, despite subtle interactions between the two caused by the weak memory model. As a corollary of the Abstraction Theorem, we establish that the proposed notion of linearizability is compositional (Corollary 5, Section 5).

To demonstrate that our notion of linearizability is appropriate for practical concurrent algorithms, we have developed a tool for systematically testing such algorithms against the definition and applied it to several examples (Section 6). We have also proved the linearizability of one of the algorithms formally (Theorem 3, Section 4). The algorithms considered are challenging to reason about and to specify, as they sometimes exhibit behaviours not reproducible on a sequentially consistent memory model.

The TSO memory model. The most intuitive way to explain the TSO memory model is operationally (Section 2), using an abstract multiprocessor machine in which every CPU has a *store buffer*. The buffer holds write requests that were issued by the CPU, but have not yet been *flushed* into the shared memory. A command that would like to write to a location in memory stores the corresponding write request in the store buffer of the CPU executing it, thus avoiding the need to block the CPU while the write completes. The CPU may decide to flush a store buffer entry into the main memory at any time, subject to maintaining the FIFO ordering of the buffer: the oldest write will be flushed first. A command that would like to read from a location in memory returns the value stored in the newest entry for this location in the store buffer of the CPU executing it; if such an entry does not exist, it accesses the memory directly.

The behaviour of programs running on TSO can sometimes be counterintuitive. For example, consider two memory locations x and y initially holding 0. On standard x86 processors, if two CPUs respectively write 1 to x and y and then read from y and x, as in the following program, it is possible for both to read 0 in the same execution:

$$x = y = 0;$$

$x = 1; b = y; || y = 1; a = x;$

$\{a = b = 0\}$

This outcome cannot happen on a sequentially consistent machine, where both reads and writes access the memory directly. On TSO, it happens when the reads from y and x occur before the writes to them have propagated from the store buffers of the corresponding CPUs to the main memory. To exclude such behaviours, TSO processors provide special instructions, called *memory barriers*, that force the store buffer of the corresponding CPU to be flushed completely before executing the next instruction. Adding memory barriers after the writes to x and y in the above program would make it produce only SC behaviours. However, barriers incur a performance penalty.

**Technical challenges.** The presence of store buffers leads to subtle interactions between a library and its client that make it challenging to define linearizability. Showing linearizability requires us to provide, for every execution of the concrete library implementation, an execution of the abstract library interacting with the client in a similar way (in a certain technical sense). Interactions between the library and the client are usually defined in terms of histories, which, in the classical definition, are sequences of calls to and returns from the library, along with the values passed. In the case of TSO, however, this would not describe all interactions between the two components, since one of them can exhibit a side effect on the other via a store buffer. For example, a memory barrier inside a library method will flush entries written there by client as well as library code. More subtly, write commands in a library method can insert entries into the store buffer without ensuring that they get flushed by the time the method returns. For this reason, on TSO, the method return point does not characterise the time by which the effects of these writes will be visible to the client (see the seqlock example in Section 4). To define the notion of linearizability on TSO that validates the Abstraction Theorem and is compositional, we thus need histories to describe the information relevant to the client about how the library uses store buffers. The classical notion of linearizability [10], which is not aware of store buffers, cannot specify this.

**Main ideas.** Our main insight lies in identifying the additional information that we need to record in histories to get a definition of linearizability on TSO validating the Abstraction Theorem. Namely, the contents of a store buffer can be viewed as a sand-wich consisting of blocks of entries inserted there by an invocation of a library method or a fragment of the client code between two such invocations. We show that the behaviour of the library with regards to the store buffer that can affect the client is completely described by the moments of time at which the first and the last elements of any given library layer in the sandwich get flushed. Roughly speaking, the time when a library layer starts to get flushed defines an assumption the library makes about the client: since store buffers are FIFO, the library requires the previous client layer in the buffer to be flushed completely before this. The time by which a library layer is flushed completely represents a guarantee the library provides to the client: this action enables the next client layer to be flushed starting from this point of time.

To specify this, we enrich histories with additional actions denoting the times when a layer of entries inserted by every library method invocation starts to get flushed and is flushed completely. Linearizability then requires preserving the order between some of these actions in a history of the concrete library implementation when providing a matching history of the abstract library implementation. As we show, this is sufficient to establish the Abstraction Theorem.

The proposed definition of linearizability on TSO requires a novel way of specifying libraries. In the classical definition, the specification of a library method often consists of one atomic action. Since on TSO writes can be delayed in the store buffer, such a specification according to our notion of linearizability is often given by two atomic actions: one that atomically writes entries into the store buffer, and one that flushes them into the memory, possibly after the method returns. The resulting specification captures the effects of using the store buffer visible to the client, yet is simpler than the implementation: it ensures that all the locations written to by a library method will be written to the memory atomically, albeit at some later time. We provide examples of such specifications in Section 4 and Appendix B.

## 2 TSO semantics

In this section, we present the operational semantics of the TSO memory model, following [14], along with our modifications to it needed to define linearizability.

**Notation.** We write  $A^+$  and  $A^*$  for the sets of all nonempty, respectively, possibly empty finite sequences of elements of a set A. We denote the empty sequence with  $\varepsilon$  and the concatenation of sequences  $\alpha_1$  and  $\alpha_2$  with  $\alpha_1\alpha_2$ . When we deal with sequences of sequences, for clarity we sometimes put an element of a sequence that is itself a sequence into brackets  $\langle \cdot \rangle$ . For example,  $\alpha_1 \langle \beta \rangle \alpha_2$  denotes a sequence containing another sequence  $\beta$  as one of its elements. We write g[x : y] for the function that has the same value as g everywhere, except for x, where it has the value y. We write \_ for an expression whose value is irrelevant and implicitly existentially quantified. We denote the powerset of a set X with  $\mathcal{P}(X)$ , and the disjoint union of sets with  $\uplus$ .

**Programming language.** We consider a machine with n CPUs, indexed by CPUid =  $\{1, \ldots, n\}$  and a shared memory. The machine executes programs of the following form:

$$L ::= \{m = C_m \mid m \in M\} \qquad C(L) ::= \text{ let } L \text{ in } C_1 \parallel \ldots \parallel C_n$$

A program consists of a declaration of a library L, implementing a set of methods  $M \subseteq$ Method, and its client, specifying a command  $C_t$  to be run by the (hardware) thread in each CPU t. For the above program we let sig(L) = M. To simplify presentation, we assume that the program is stored separately from the memory.

It is technically convenient for us to abstract from a particular syntax of thread and method bodies  $C_t$  and  $C_m$  and represent them using *control-flow graphs*. Namely, assume a set of primitive commands PComm (defined below). A control-flow graph (CFG) over the set PComm is a tuple (N, T, start, end), consisting of the set of program positions N, the control-flow relation  $T \subseteq N \times \text{PComm} \times N$ , and the initial and final positions start, end  $\in N$ . The edges of the CFG are annotated with primitive commands from PComm.

We represent a program C(L) by a collection of CFGs: the client command  $C_t$ for a CPU t is represented by  $(N_t, T_t, \text{start}_t, \text{end}_t)$ , and the body  $C_m$  of a method m by  $(N_m, T_m, \text{start}_m, \text{end}_m)$ . We often view this collection of CFGs for C(L) as a single graph consisting of the node set  $N = \bigcup_{t=1}^n N_t \uplus \bigcup_{m \in \text{sig}(L)} N_m$  and the edge set  $T = \bigcup_{t=1}^n T_t \uplus \bigcup_{m \in \text{sig}(L)} T_m$ .

**Machine configurations.** The set of possible configurations Config of our machine is defined in Figure 1. The special configuration  $\top$  results from the machine executing an illegal instruction, such as dereferencing a non-existent memory location. An ordinary configuration  $(pc, \theta, b, h, K) \in Config consists of several components. The first one <math>pc \in CPUid \rightarrow Pos$  gives the current instruction pointer of every CPU. When a CPU executes client code, its instruction pointer defines the program position of the client command being executed. Otherwise, it is given by a pair whose first component is the program position of the current library command, and the second one is the client position to return to when the library method finishes executing (one return position is sufficient, since, as explained below, we disallow nested method calls).

$\begin{array}{ll} \mathsf{Loc} = \mathbb{N} & \mathsf{Val} = \mathbb{Z} \\ \mathsf{Pos} = N \uplus (N \times N) & \mathsf{Reg} = \{\mathtt{r}_1, \dots, \mathtt{r}_m\} \\ \mathsf{Buff} = ((\mathsf{Loc} \times \mathsf{Val})^+ \cup \{\mathsf{lock}, \mathsf{call}, \mathsf{ret}\})^* \\ \mathsf{Config} = \{\top\} \cup ((\mathsf{CPUid} \to \mathsf{Pos}) \times (\mathsf{CPUid} \to \mathsf{RegBank}) \times \\ & (\mathsf{CPUid} \to \mathsf{Buff}) \times \mathsf{Heap} \times \mathcal{P}(\mathsf{CPUid})) \end{array}$

$\begin{array}{l} \mathsf{Heap} = \mathsf{Loc} \rightharpoonup_{\mathit{fin}} \mathsf{Val} \\ \mathsf{RegBank} = \mathsf{Reg} \rightarrow \mathsf{Val} \end{array}$

Fig. 1. The set of machine configurations

Each CPU in the machine has a set of registers Reg, whose values are defined by  $\theta \in \text{CPUid} \rightarrow \text{RegBank}$ . The machine memory  $h \in \text{Heap}$  is represented as a finite partial function from existing memory locations to the values they store. The component  $K \in \mathcal{P}(\text{CPUid})$  defines the set of *active* CPUs that can currently execute a command and is used to implement atomic execution of certain commands.

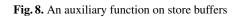

The component  $b \in CPUid \rightarrow Buff$  describes the state of all store buffers in the machine, each represented by a sequence of write requests with newest coming first. The contents of store buffers in our configurations differ from those prescribed by the TSO memory model [14] in two ways.

First, in TSO every entry in a store buffer is represented by a single location-value pair, whereas we use a sequence of those. In our semantics, all the locations in such a sequence are written to the memory atomically. This functionality is not provided by the hardware; we use it for expressing the semantics of library specifications, which might include atomic blocks performing several writes (see the seqlock example in Section 4).

Second, to formulate linearizability, we need to maintain some auxiliary information about executions, recorded by call, ret and lock entries in a store buffer. The marker lock is used to implement atomic commands performing several writes to different locations in memory. The markers call and ret get added to the buffer upon a call to or a return from the library, respectively, and thus delimit entries added by library method invocations and client code. They are used to generate additional actions in histories of interactions between the client and the library needed to define linearizability on TSO. We note that, despite store buffers in our configurations including call and ret markers, the semantics we define below corresponds to the standard TSO one, in the sense that erasing the markers from store buffers in all configurations of a given execution yields a valid execution in the standard TSO semantics.

**Primitive commands.** The set of primitive commands is defined as follows:

$\mathsf{PComm} = \mathsf{Local} \uplus \mathsf{Read} \uplus \mathsf{Write} \uplus \{m \mid m \in \mathsf{Method}\} \uplus \{\mathsf{lock}, \mathsf{unlock}, \mathsf{xlock}, \mathsf{xunlock}\}.$

Here Local, Read and Write are unspecified sets of commands such that:

- commands in Local access only CPU registers;

- commands in Read read a single location in memory and write its contents into the register r<sub>1</sub>;

- commands in Write write to a single location in memory.

We also have library method calls and the commands lock and unlock that lock the machine, allowing several commands to be executed atomically, and unlock it. We assume that parameters and return values of methods are passed via CPU registers. If a

client needs to preserve register values when calling a library method, it can save them in memory before the call and restore them when the method returns. The xlock and xunlock commands act as lock and unlock, except they have a built-in memory barrier, flushing the store buffer of the CPU executing the command. We call a sequence of commands bracketed by lock and unlock, or xlock and xunlock, an *atomic block*.

For every command  $c \in \mathsf{Local} \uplus \mathsf{Read} \uplus \mathsf{Write}$ , we assume a transformer:

- $f_c$ : RegBank  $\rightarrow \mathcal{P}(\text{RegBank})$  for  $c \in \text{Local defining how the command changes}$ the registers of the CPU executing it;

- $f_c$ : RegBank  $\rightarrow \mathcal{P}(\mathsf{Loc})$  for  $c \in \mathsf{Read}$  defining the location read;

- $f_c$ : RegBank  $\rightarrow \mathcal{P}(Loc \times Val)$  for  $c \in Write$  defining the location and the value written.

Note that we allow the execution of primitive commands to be non-deterministic. As in this paper we are dealing with low-level programs, we do not assume a built-in allocator, and thus do not consider commands for memory (de)allocation as primitive.

We place certain restrictions on CFGs over the above set PComm. Namely, we assume that on any path in a CFG, (x)lock and (x)unlock commands alternate correctly. In particular, we disallow nested (x)lock instructions. We assume that every method called in the program is defined, and we disallow nested method calls as well as method calls inside atomic blocks.

Let E, F denote expressions over the set of registers Reg, and  $\llbracket E \rrbracket r$  the result of evaluating the expression E in the register bank r. Then we can define sample primitive commands

havoc  $\in$  Local, assume $(E) \in$  Local, read $(E) \in$  Read, write $(E, F) \in$  Write

with the following semantics:

| $f_{havoc}(r) = RegBank;$                                                           | $f_{assume(E)}(r) = \{r\},\$    | if $\llbracket E \rrbracket r \neq 0$ ; |

|-------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------|

| $f_{read(E)}(r) = \{\llbracket E \rrbracket r\};$                                   | $f_{assume(E)}(r) = \emptyset,$ | if $[\![E]\!]r = 0;$                    |

| $f_{write(E,F)}(r) = \{ (\llbracket E \rrbracket r, \llbracket F \rrbracket r) \}.$ |                                 |                                         |

The read and write commands have the expected meaning. The havoc command assigns arbitrary values to all registers. The  $\operatorname{assume}(E)$  command acts as a filter on states, choosing only those where E evaluates to non-zero values. Using  $\operatorname{assume}(E)$ , a conditional branch on the value of E can be implemented with the CFG edges  $(v, \operatorname{assume}(E), v_1)$  and  $(v, \operatorname{assume}(!E), v_2)$ , where !E denotes the C-style negation.

Given the above commands, a memory barrier can be implemented as "xlock; xunlock". We can also implement the well-known atomic compare-and-swap (CAS) operation. A CAS takes three arguments: a memory address addr, an expected value v1 and a new value v2. It atomically reads the memory address and updates it with the new value when the address contains the expected value; otherwise, it does nothing. In our language, we define CAS(addr, v1, v2) as syntactic sugar for the control-flow graph representation of:

```

xlock;

if (*addr == v1) { *addr = v2; xunlock; return 1; }

else { xunlock; return 0; }

```

Actions and traces. Transitions in our operational semantics are labelled using *actions* of the form

$$\begin{split} \varphi \in \mathsf{Act} ::= (t, \mathsf{read}(x, u)) \mid (t, \mathsf{write}(x, u)) \mid (t, \mathsf{flush}(x, u)) \mid (t, \mathsf{flush}(\mathsf{call})) \mid \\ (t, \mathsf{flush}(\mathsf{ret})) \mid (t, \mathsf{lock}) \mid (t, \mathsf{unlock}) \mid (t, \mathsf{xlock}) \mid (t, \mathsf{xunlock}) \mid \\ (t, \mathsf{call} \ m(r)) \mid (t, \mathsf{ret} \ m(r)) \end{split}$$

where  $t \in CPUid$ ,  $x \in Loc$ ,  $u \in Val$ ,  $m \in Method$  and  $r \in RegBank$ . Here (t, write(x, u)) corresponds to enqueuing a pending write of u to the location x into the store buffer of CPU t, (t, flush(x, u)) to flushing a pending write of u to the location x from the store buffer of t into the shared memory, (t, flush(call)) or (t, flush(ret)) to discarding a call or ret marker from the head of a store buffer. The last two actions record moments of time when entries in a store buffer written by a given library method invocation start to get flushed and are flushed completely, which are needed in the formulation of linearizability as we explained in Section 1. The rest of the actions have the expected meaning. Since parameters and return values of library methods are passed via CPU registers, we record their values in call and return actions.

We call a (finite or infinite) sequence of actions a *trace* and adopt the standard notation:  $\lambda(i)$  is the *i*-th action in the trace  $\lambda$ ,  $|\lambda|$  is the length of the trace  $\lambda$  ( $|\lambda| = \omega$  if  $\lambda$  is infinite), and  $\lambda|_t$  is the projection of  $\lambda$  to actions by CPU t.

**Program semantics.** The operational semantics of a program C(L) is defined by the transition relation  $\longrightarrow_{C(L)}$ : Config  $\times \operatorname{Act}^* \times \operatorname{Config}$  in Figure 2. We remind the reader that T in the figure is the control-flow relation of C(L). To handle transitions inside the library code, we lift it to program positions  $N \uplus (N \times N)$  as follows:

$$\hat{T} = T \cup \{ ((v, v_0), c, (v', v_0)) \mid (v, c, v') \in T \land v_0 \in N \}.$$

The LOCAL rule handles the execution of commands that access registers only. These and other commands can only be executed by a CPU t if it is included into the set of active CPUs, represented by the last component of a configuration.

A write by a CPU to a location in memory does not happen immediately; instead, a pair of the location and the value to be written is added to the tail of the corresponding store buffer (WRITE). Recall that the newest entry comes first in the store buffer. When the location being written does not exist, the write command faults (WRITE- $\top$ ).

The READ rule uses  $lookup(\alpha, h, x)$  to find the value stored for the address x in the store buffer  $\alpha$  of the CPU executing the command or the memory h:

$$\mathsf{lookup}(\alpha, h, x) = \begin{cases} u, & \text{if } \alpha = \alpha_1 \langle \beta_1 (x, u) \beta_2 \rangle \alpha_2 \text{ and} \\ \alpha_1, \beta_1 \text{ do not contain entries for } x; \\ h(x), & \text{if } x \in \mathsf{dom}(h) \text{ and } \alpha \text{ does not contain entries for } x; \\ \top, & \text{otherwise.} \end{cases}$$

If there are entries for x in the store buffer, the read takes the value in the newest one; otherwise, it looks up the value in memory. If the location being read does not exist, lookup returns  $\top$ . According to READ, the value read is stored in the register  $r_1$ .

| $\frac{t \in K  (\rho, c, \rho') \in \hat{T}  c \in Local  r' \in f_c(r)}{pc[t:\rho], \theta[t:r], b, h, K \xrightarrow{\varepsilon}_{C(L)} pc[t:\rho'], \theta[t:r'], b, h, K}  LOCAL$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $(\rho, c, \rho') \in \hat{T} \qquad c \in Write \qquad (x, u) \in f_c(r) \qquad x \in dom(h)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $pc[t:\rho], \theta[t:r], b[t:\alpha], h, K \xrightarrow{(t,write(x,u))}_{C(L)} pc[t:\rho'], \theta[t:r], b[t:(x,u)\alpha], h, K$ $WRITE$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $\frac{t \in K \qquad (\rho, c, \rho') \in \hat{T} \qquad c \in Write \qquad (x, u) \in f_c(r) \qquad x \not\in dom(h)}{pc[t:\rho], \theta[t:r], b, h, K \xrightarrow{\varepsilon}_{C(L)} \top} \qquad WRITE- \top$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $\underbrace{t \in K \qquad (\rho, c, \rho') \in \hat{T} \qquad c \in Read \qquad x \in f_c(r) \qquad u = lookup(\alpha, h, x) \neq \top}_{(I or (I or $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $pc[t:\rho], \theta[t:r], b[t:\alpha], h, K \xrightarrow{(t,read(x,u))}_{C(L)} pc[t:\rho'], \theta[t:r[\mathbf{r}_1:u]], b[t:\alpha], h, K \xrightarrow{READ}_{C(L)} pc[t:\rho'], \theta[t:r[\mathbf{r}_1:u]], h, K \xrightarrow{READ}_{C(L)} pc[t:r[\mathbf{r}_1:u]], h, K $ |

| $\frac{t \in K \qquad (\rho, c, \rho') \in \hat{T} \qquad c \in Read \qquad x \in f_c(r) \qquad lookup(\alpha, h, x) = \top}{pc[t:\rho], \theta[t:r], b[t:\alpha], h, K \xrightarrow{\varepsilon}_{C(L)} \top} \qquad Read-T$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $\frac{(\rho, lock, \rho') \in \hat{T}}{pc[t:\rho], \theta, b[t:\alpha], h, CPUid} \xrightarrow{(t, lock)}_{C(L)} pc[t:\rho'], \theta, b[t:lock\alpha], h, \{t\}}  Lock$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $( ho, unlock,  ho') \in \hat{T}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $pc[t:\rho], \theta, b[t:(x_1, u_1) \dots (x_l, u_l) lock \alpha], h, \{t\} \xrightarrow{(t,unlock)}_{C(L)} pc[t:\rho'], \theta, b[t:\langle (x_1, u_1) \dots (x_l, u_l) \rangle \alpha], h, CPUid$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $ \begin{array}{l} pc, \theta, b[t: \alpha \left\langle (x_1, u_1) \dots (x_l, u_l) \right\rangle], h, CPUid \xrightarrow{(t, flush(x_l, u_l)) \dots (t, flush(x_1, u_1))}{pc, \theta, b[t: \alpha], h[x_l: u_l] \dots [x_1: u_1], CPUid} \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $\frac{\beta \in \{\text{call}, \text{ret}\}}{(1.8 \times 10^{\circ})}$ Flush-Marker                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $pc, \theta, b[t:\alpha\beta], h, CPUid \xrightarrow{(t,flush(\beta))}_{C(L)} pc, \theta, b[t:\alpha], h, CPUid$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $(\rho, xlock, \rho') \in \hat{T} $ XLock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $pc[t:\rho], \theta, b[t:\varepsilon], h, CPUid \xrightarrow{(t,xlock)}_{C(L)} pc[t:\rho'], \theta, b[t:\varepsilon], h, \{t\}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $(\rho,xunlock,\rho')\in\hat{T}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $ \begin{array}{c} pc[t:\rho], \theta, b[t:(x_1, u_1) \dots (x_l, u_l)], h, \{t\} \xrightarrow{(t, flush(x_l, u_l)) \dots (t, flush(x_1, u_1))(t, xunlock)} \\ pc[t:\rho'], \theta, b[t:\varepsilon], h[x_l:u_l] \dots [x_1:u_1], CPUid \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XUNLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $\frac{(v, m, v') \in T}{(t, call \ m(r))}  CALL$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $pc[t:v], \theta[t:r], b[t:\alpha], h, CPUid \xrightarrow{(t,call  m(r))}_{C(L)} pc[t:(start_m, v')], \theta[t:r], b[t:call  \alpha], h, CPUid$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |