Under consideration for publication in J. Functional Programming

# Modular Verification of Preemptive OS Kernels

ALEXEY GOTSMAN IMDEA Software Institute

HONGSEOK YANG University of Oxford

# Abstract

Most major OS kernels today run on multiprocessor systems and are preemptive: it is possible for a process running in the kernel mode to get descheduled. Existing modular techniques for verifying concurrent code are not directly applicable in this setting: they rely on scheduling being implemented correctly, and in a preemptive kernel, the correctness of the scheduler is interdependent with the correctness of the code it schedules. This interdependency is even stronger in mainstream kernels, such as those of Linux, FreeBSD or Mac OS X, where the scheduler and processes interact in complex ways.

We propose the first logic that is able to decompose the verification of preemptive multiprocessor kernel code into verifying the scheduler and the rest of the kernel separately, even in the presence of complex interdependencies between the two components. The logic hides the manipulation of control by the scheduler when reasoning about preemptable code and soundly inherits proof rules from concurrent separation logic to verify it thread-modularly. We illustrate the power of our logic by verifying an example scheduler, which includes some of the key features of the scheduler from Linux 2.6.11 challenging for verification.

#### 1 Introduction

Developments in formal verification now allow us to consider the full verification of an operating system (OS) kernel, one of the most crucial components in any system today. Several recent projects have demonstrated that formal verification of can tackle realistic OS kernels, such as a variant of the L4 microkernel (Klein *et al.*, 2009) and Microsoft's Hyper-V hypervisor (Cohen *et al.*, 2010). However, these projects only dealt with relatively small microkernels; tackling today's mainstream operating systems, such as Windows and Linux, remains a daunting task. A way to approach this problem is to verify OS kernels *modularly*, i.e., by considering each of their components in isolation. In this paper, we tackle a major challenge OS kernels present for modular reasoning—handling kernel preemption in a multiprocessor system. Most major OS kernels are designed to run with multiple CPUs and are *preemptive*: it is possible for a process running in the kernel mode to get descheduled. Reasoning about such kernels is difficult for the following reasons.

First of all, in a multiprocessor system several invocations of a system call may be running concurrently in a shared address space, so reasoning about the call needs to consider all possible interactions among them. This is a notoriously difficult problem; however, we now have a number of logics that can reason about concurrent code (O'Hearn,

### Alexey Gotsman and Hongseok Yang

2007; Gotsman *et al.*, 2007; Feng *et al.*, 2007a; Vafeiadis & Parkinson, 2007; Dinsdale-Young *et al.*, 2010; Cohen *et al.*, 2010; Dinsdale-Young *et al.*, 2013). The way the logics make verification tractable is by using *thread-modular* reasoning principles that consider every thread of computation in isolation under some assumptions about its environment and thus avoid direct reasoning about all possible interactions (Jones, 1983; Pnueli, 1985).

The problem is that all these logics can verify code only under so-called interleaving semantics, expressed by the well-known operational semantics rule:

$$\frac{C_k \longrightarrow C'_k}{C_1 \parallel \ldots \parallel C_k \parallel \ldots \parallel C_n \longrightarrow C_1 \parallel \ldots \parallel C'_k \parallel \ldots \parallel C_n}$$

This rule effectively assumes an abstract machine where every process  $C_k$  has its own CPU, whereas in an OS, the processes are multiplexed onto available CPUs by a scheduler, which is part of the OS kernel. Furthermore, in a preemptive kernel, the correctness of the scheduler is *interdependent* with the correctness of the rest of the kernel (which, in the following, we refer to as just the kernel). This is because, when reasoning about a system call implementation in a preemptive kernel, we have to consider the possibility of context-switch code getting executed at almost every program point. Upon a context switch, the state of the system call will be stored in kernel data structures and subsequently loaded for execution again, possibly on a different CPU. A bug in the context switch, and a bug in the system call can corrupt the scheduler's data structures. It is, of course, possible to reason about the kernel together with the scheduler as a whole, using one of the available logics. However, in a mainstream kernel, where kernel preemption is enabled most of the time, such reasoning would quickly become intractable.

**Contributions.** In this paper we propose a logic that is able to decompose the verification of safety properties of preemptive OS code into verifying preemptable code and the scheduler (including the context-switch code) separately. This is the first logic that can achieve this in the presence of interdependencies between the scheduler and the kernel typical for mainstream OS kernels, such as those of Linux, FreeBSD and Mac OS X. The modularity of the logic is reflected in the structure of its proof system, which is partitioned into high-level and low-level parts. The high-level proof system verifies preemptable code assuming that the scheduler is implemented correctly (Section 5.2). It hides the complex manipulation of control by the context-switch code, which stores program counters of processes, describing their continuations, and jumps to one of them. In this way, the high-level proof system provides the illusion of an abstract machine where every process has its own virtual CPU—the control moves from one program point in the process code to the next without changing its state. This illusion is justified by verifying the scheduler code separately from the kernel in the low-level proof system (Section 5.3). Achieving this level of modularity requires us to cope with several technical challenges.

First, the setting of a preemptive OS kernel introduces an obligation to prove that the scheduler and the kernel do not corrupt each other's data structures. A common way to achieve this is by introducing the notion of *ownership* of memory areas: only the component owning an area of memory has the right to access it (Clarke *et al.*, 2001; Reynolds, 2002). A major difficulty of decomposing the verification of the mainstream

OS kernels mentioned above lies in the fact that, in such kernels, there is no static address space separation between data structures owned by the scheduler and the rest of the kernel: the boundary between these changes according to a protocol for transferring the ownership of memory cells and permissions to access them in a certain way. For example, when an implementation of the fork system call asks the scheduler to make a new process runnable, the scheduler usually gains the ownership of the process descriptor provided by the system call implementation.

To deal with this, we base our proof systems on concurrent separation logic (O'Hearn, 2007), which we recap in Section 4. The logic allows us to track the dynamic memory partitioning between the scheduler and the rest of the kernel and prohibit memory accesses that cross the partitioning boundary. For example, assertions in the high-level proof system talk only about the memory belonging to the kernel and completely hide the memory belonging to the scheduler. A *frame property*, validated by concurrent separation logic, implies that in this case any memory not mentioned in the assertions, e.g., the memory belonging to the scheduler, is guaranteed not to be changed by the kernel. A realistic interface between the scheduler and the kernel is supported by proof rules for ownership transfer of logical assertions between the two components, describing permissions to access memory cells.

Using an off-the-shelf logic, however, is not enough to prove the correctness of a scheduler, as this requires domain-specific reasoning: e.g., we need to be able to check that a scheduler restores the state of a preempted process correctly when it resumes the process. To this end, the low-level proof system for reasoning about schedulers includes special Process assertions about the continuation of every OS process the scheduler manages, describing the states from which it can be safely resumed. A novelty of these assertions affinely and allows us to interpret them as exclusive permissions to schedule the corresponding processes. This enables reasoning about scheduling on multiprocessors, as it allows checking that the scheduler invocations on different CPUs coordinate decisions about process scheduling correctly. Another interesting feature of Process assertions is that they describe only the part of the process state the scheduler is supposed to access and hide the rest; this ensures that the scheduler indeed cannot corrupt the latter. In this our Process assertions are similar to abstract predicates (Parkinson & Bierman, 2005).

Even though a scheduler is supposed to provide an illusion of running on a dedicated *virtual* CPU to every process, in practice, some features available to the kernel code can break through this abstraction: e.g., a process can disable preemption and become aware of the *physical* CPU on which it is currently executing. For example, some OS kernels use this to implement *per-CPU data structures* (Bovet & Cesati, 2005)—arrays indexed by CPU identifiers such that a process can only access an entry in an array when it runs on the corresponding CPU. We demonstrate that our approach can deal with such implementation exposures by extending the high-level proof system for the kernel code with axioms that allow reasoning about per-CPU data structures (Section 7).

In reasoning about mainstream operating systems, assertions describing the state transferred between the scheduler and the kernel can be complicated. The resulting ownership transfers make even formalising the notion of scheduler correctness non-trivial, as they are difficult to accommodate in an operational semantics of the abstract machine

# Alexey Gotsman and Hongseok Yang

with one CPU per process the scheduler is supposed to implement (Gotsman *et al.*, 2011). We resolve this problem in the following way. In our logic, the desired properties of OS code are proved with respect to the abstract machine using the high-level proof system; the low-level system then relates the concrete and the abstract machines. However, proofs in neither of the two systems are interpreted with respect to any semantics alone. Instead, our soundness statement (Section 8) interprets a proof of the kernel in the high-level system and a proof of the scheduler in the low-level one together with respect to the semantics of the concrete machine. To this end, the statement has to construct a global property of the machine from local assertions about OS components in a non-trivial way.

Even though all of the OS verification projects carried out so far had to deal with a scheduler (see Section 9 for a discussion), to our knowledge they have not produced methods for handling practical multiprocessor schedulers with a complicated scheduler/kernel interface. We illustrate the power of our logic by verifying an example scheduler (Sections 2.2 and 6), which includes some of the key features of the scheduler from Linux 2.6.11 exhibiting the issues mentioned above.

**Limitations.** Our goal here is not to verify an industrial-strength preemptive OS kernel such an endeavour is beyond the scope of a single paper. Rather, we develop *principles* of how a given logic for verifying concurrent programs can be extended to verify preemptive kernel code with *real-world features*. These principles can then be used in verification projects that target different operating systems. To communicate the proposed principles cleanly and understandably, we present our results in a simplified setting:

- Instead of a realistic processor, such as x86, we consider an idealised machine (Sections 2.1 and 3).

- Since we are primarily interested in interactions of components within an OS kernel, our machine does not make a distinction between the user mode and the kernel mode.

- We base our logic for verifying OS kernels on one of the simplest logics for concurrent code—concurrent separation logic (O'Hearn, 2007). This logic would not be able to handle complicated concurrency mechanisms employed in modern OS kernels (Bovet & Cesati, 2005). However, as we argue in Section 8.2, our development can be adapted to its more advanced derivatives (Gotsman *et al.*, 2007; Feng *et al.*, 2007a; Vafeiadis & Parkinson, 2007; Dinsdale-Young *et al.*, 2010; Dinsdale-Young *et al.*, 2013).

- Since we concentrate on modular reasoning about concurrency and preemptive scheduling, our logic provides only rudimentary means of modular reasoning about sequential code and, in particular, procedures. We discuss ways of addressing this problem in Section 10.

- We consider scheduling interfaces providing only the basic services—context switch and process creation. We discuss how our logic can be extended to schedulers with more elaborate interfaces in Sections 5.5 and 10.

- Due to our focus on scheduling, we ignore many other aspects of an OS kernel, such as virtual memory and interrupts not related to scheduling.

- Our logic is designed for proving safety properties only. Proof methods for liveness properties usually rely on modular methods for safety properties. Thus, our logic is a prerequisite for attacking liveness in the future.

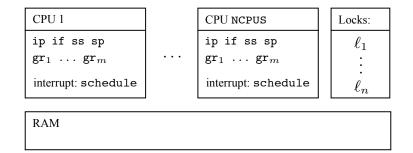

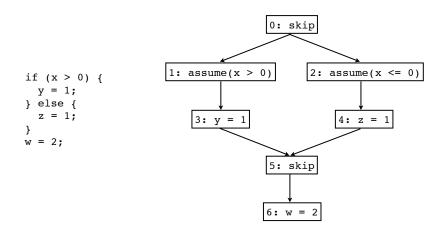

Fig. 1. The target machine

Even though we develop our logic in this simplified setting, we hope that its modular nature makes it more likely that it will compose with logics for features and abstractions that we currently do not handle. A preliminary indication of this is our ability to deal with per-CPU data structures, despite the fact that these break through the abstraction implemented by a scheduler.

#### 2 Informal development

We first explain our results informally, sketching the machine we use for formalising them (Section 2.1), illustrating the challenges of reasoning about schedulers by an example (Section 2.2) and describing the approach we take in our program logic (Section 2.3).

# 2.1 Example machine

We formalise our results for a simple machine, defined in Section 3. Here we present it informally to the extent needed for understanding the rest of this section. We summarise its features in Figure 1.

The machine has multiple CPUs, identified by integers from 1 to NCPUS, communicating via the shared memory. We assume that the program the machine executes is stored separately from the heap and may not be modified; its commands are identified by labels. For simplicity we also assume that programs can synchronise using a set of built-in locks (in a real system they would be implemented as spin-locks). Every CPU has a single interrupt, with its handler located at a distinguished label schedule (the same for all CPUs). A scheduler can use the interrupt to trigger a context switch. There are four special-purpose registers, ip, if, ss and sp, and *m* general-purpose ones,  $gr_1, \ldots, gr_m$ . The ip register is the instruction pointer. The if register controls interrupts: they are disabled on the corresponding CPU when if stores zero, and enabled otherwise. As if affects only one CPU, we might have several instances of the scheduler code executing in parallel on different CPUs. Upon an interrupt, the CPU sets if to 0, which prevents nested interrupts. The ss register keeps the starting address of the stack, and sp points to the top of the stack, i.e., its first free slot. The stack grows upwards, so we always have ss  $\leq$  sp. As we noted before, our machine does not make a distinction between the user mode and the

# Alexey Gotsman and Hongseok Yang

kernel mode—all processes can potentially access all available memory and execute all commands.

The machine executes programs in a minimalistic assembly-like programming language. It is described in full in Section 3; for now it suffices to say that the language includes standard commands for accessing registers and memory, and the following special ones:

- $lock(\ell)$  and  $unlock(\ell)$  acquire and release the lock  $\ell$ .

- savecpuid(*e*) stores the identifier of the CPU executing it at the address *e*.

- call(*l*) is a call to the function that starts at the label *l*. It pushes the label of the next instruction in the program and the values of the general-purpose registers onto the stack, and jumps to the label *l*.

- icall(*l*) behaves the same as call(*l*), except that it also disables interrupts by modifying the if register.

- ret is the return command. It pops the return label and the saved general-purpose registers off the stack, updates the registers with the new values, and jumps to the return label.

- iret is a variant of ret that additionally enables interrupts.

When the if register is set to a non-zero value, an interrupt can fire at any time. This has the same effect as executing icall(schedule).

# 2.2 Motivating example

**The challenge.** Figures 2–3 present an implementation of the scheduler that we use as a running example. Our goal is to be able to verify safety properties of OS processes managed by this scheduler using off-the-shelf concurrency logics, i.e., as though every process has its own virtual CPU. To show what this entails, consider the piece of code in Figure 4 (page 10), which could be a part of a system call implementation in the kernel (we explain its proof later). The code removes some of the nodes from a cyclic doubly-linked list with a sentinel head node pointed to by request\_queue. Here and in the following, we use some library functions: e.g., remove\_node deletes a node from the doubly-linked list it belongs to. We assume that the code can be called concurrently by multiple processes, and thus protect the list with a lock request\_lock: the list can only be accessed by the process that holds this lock.

There are a number of properties we might want to prove about this code: e.g., that pointer manipulations done by the invocation of remove\_node in line 25 do not overwrite a memory cell storing critical information elsewhere in the kernel, or that the doubly-linked list shape of request\_queue is preserved. Modern concurrency logics can prove such properties by considering every process in isolation. Namely, every assertion in Figure 4 describes information about the state of the program relevant to the process executing the code. These assertions are justified using essentially sequential reasoning, and in particular, using the classical proof rule for sequential composition:

$$\frac{\{P_1\} C_1 \{P_2\} \{P_2\} C_2 \{P_3\}}{\{P_1\} C_1; C_2 \{P_3\}}$$

(1)

We would like such reasoning (and the proof in Figure 4) to be sound even when the code is managed by the scheduler in Figures 2–3. Hence, we need to be able to ignore the fact that

6

the control flow of the code in Figure 4 can jump to the schedule function in Figure 2 at any time, with the state of the former stored in kernel data structures and loaded from them again later. Furthermore, we need to achieve this even though the scheduler and the system call implementation execute in a shared address space and can thus potentially access each other's data structures.

**Example scheduler.** The example scheduler in Figures 2-3 includes some of the key features of the scheduler from Linux 2.6.11 (Bovet & Cesati, 2005) that are challenging for verification, as detailed below.<sup>1</sup>

The scheduler's interface consists of two functions: schedule and create. The former is called as the interrupt handler or directly by a process and is responsible for switching the process running on the CPU and migrating processes between CPUs. The latter can be called by the kernel implementation of the fork system call and is responsible for inserting a newly created process into the scheduler's data structures, thereby making it runnable. Both functions are called by processes using the icall command that disables interrupts, so that the scheduler routines always execute with interrupts disabled.

**Programming language.** Even though we formalise our results for a machine executing a minimalistic programming language, we present the example in C. We now explain how a C program, such as the one in Figures 2–3, is mapped to our machine.

We assume that every global variable x is allocated at a fixed address &x in memory. Local variable declarations allocate local variables on the stack in the activation records of the corresponding procedures; these variables are then addressed via the sp register. When the variables go out of scope, they are removed from the stack by decrementing the sp register. The general-purpose registers are used to store intermediate values while computing complex expressions. In our C programs, we allow the ss and sp registers to be accessed directly as \_ss and \_sp. Function calls and returns are implemented using the call and ret commands of the machine. By default, parameters and return values are passed via the stack; in particular, a zero-filled slot for a return value is allocated on the stack before calling a function. Parameters of functions annotated with \_regparam (such as create, line 64 in Figure 3) are passed via registers. We assume macros lock, unlock, savecpuid and iret for the corresponding machine commands.

**Data structures.** Every process is associated with a process descriptor of type Process. Its prev and next fields are used by the scheduler to connect descriptors into doubly-linked lists of processes it manages (*runqueues*). The scheduler uses per-CPU runqueues with dummy head nodes pointed to by the entries in the runqueue array. These are protected by the locks in the runqueue\_lock array. The entries in the current array point to the descriptors of the processes running on the corresponding CPUs; these descriptors are not members of any runqueue. Thus, every process descriptor is either in the current

<sup>&</sup>lt;sup>1</sup> We took an older version of the Linux kernel (from 2005) as a reference because its scheduler uses simpler data structures. Newer versions use more efficient data structures (Love, 2010) that would only complicate our running example without adding anything interesting.

Alexey Gotsman and Hongseok Yang

```

#define StackSize ... // size of the stack

1

#define FORK_FRAME sizeof(Process*)

2

#define SCHED_FRAME sizeof(Process*)+sizeof(int)

struct Process {

5

Process *prev, *next;

word kernel_stack[StackSize];

word *saved_sp;

int timeslice;

};

10

11

Lock *runqueue_lock[NCPUS];

12

Process *runqueue[NCPUS];

13

Process *current[NCPUS];

14

15

void init() {

16

for (int cpu = 0; cpu < NCPUS; cpu++) {</pre>

17

Process* dummy = alloc(sizeof(Process));

18

Process* process0 = alloc(sizeof(Process));

19

dummy->prev = dummy->next = dummy;

20

process0->timeslice = SCHED_QUANTUM;

21

... // initialise the stack of process0

22

runqueue[cpu] = dummy;

23

current[cpu] = process0;

24

}

25

}

26

27

void schedule() {

28

29

int cpu;

Process *old_process;

30

savecpuid(&cpu);

31

load_balance(cpu);

32

old_process = current[cpu];

33

... // update the timeslice of old_process

34

if (old_process->timeslice) iret();

35

old_process->timeslice = SCHED_QUANTUM;

36

lock(runqueue_lock[cpu]);

37

insert_node_after(runqueue[cpu]->prev, old_process);

38

current[cpu] = runqueue[cpu]->next;

39

remove_node(current[cpu]);

40

old_process->saved_sp = _sp;

41

_sp = current[cpu]->saved_sp;

42

savecpuid(&cpu);

43

_ss = current[cpu]->kernel_stack;

44

unlock(runqueue_lock[cpu]);

45

iret();

46

}

47

```

Fig. 2. The example scheduler (continued in Figure 3)

```

void load_balance(int cpu) {

47

48

int cpu2;

49

Process *proc;

if (random(0, 1)) return;

50

do { cpu2 = random(0, NCPUS-1); } while (cpu == cpu2);

51

if (cpu < cpu2) {

52

lock(runqueue_lock[cpu]); lock(runqueue_lock[cpu2]); }

53

else { lock(runqueue_lock[cpu2]); lock(runqueue_lock[cpu]); }

54

if (runqueue[cpu2]->next != runqueue[cpu2]) {

55

proc = runqueue[cpu2]->next;

56

remove_node(proc);

57

insert_node_after(runqueue[cpu], proc);

58

}

59

unlock(runqueue_lock[cpu]);

60

unlock(runqueue_lock[cpu2]);

61

}

62

63

_regparam void create(Process *new_process) {

64

int cpu;

65

savecpuid(&cpu);

66

new_process->timeslice = SCHED_QUANTUM;

67

lock(runqueue_lock[cpu]);

insert_node_after(runqueue[cpu], new_process);

69

unlock(runqueue_lock[cpu]);

70

iret();

71

}

72

73

int fork() {

74

75

Process *new_process;

new_process = alloc(sizeof(Process));

76

memcpy(new_process->kernel_stack, _ss, StackSize);

77

new_process->saved_sp = new_process->kernel_stack+

78

_sp-_ss-FORK_FRAME+SCHED_FRAME;

79

_icall create(new_process);

80

return 1;

81

}

82

```

Fig. 3. The example scheduler (continued)

array or in some runqueue. Note that every CPU always has at least one process to run the one in the corresponding slot of the current array. Every process has its own kernel stack of a fixed size StackSize, represented by the kernel\_stack field of its descriptor. When a process is preempted, the saved\_sp field is used to save the value of the stack pointer register sp; the other registers are saved on the stack. Finally, while a process is running, the timeslice field gives the remaining time from its scheduling time quantum and is periodically updated by the scheduler. The init function in Figure 2 sketches code that could be used to initialise the scheduler data structures.

Apart from the data structures described above, a realistic kernel would contain many others not related to scheduling, including additional fields in process descriptors. The kernel data structures reside in the same address space as the ones belonging to the

Alexey Gotsman and Hongseok Yang

```

#define StackSize ... // size of the stack

struct Request {

Request *prev, *next;

int data;

};

Request *request_queue; // a cyclic doubly-linked list with a sentinel node

Lock *request_lock; // protects the list

. . .

Request *req, *tmp;

10

\{reg \Vdash sp..(ss + StackSize - 1) \mapsto \land sp = ss + 2 \cdot sizeof(Request*)\}

11

lock(request_lock);

12

\{req \Vdash \exists x, y, z. \& \texttt{request\_queue} \mapsto z * z. \texttt{prev} \mapsto y * z. \texttt{next} \mapsto x * z. \texttt{data} \mapsto \_ *

13

dll_{\Lambda}(x,z,z,y) * locked(request_lock) *

14

sp..(ss + StackSize - 1) \mapsto \land sp = ss + 2 \cdot sizeof(Request*)

15

req = request_queue->next;

\{req \Vdash \exists y, z. \& request\_queue \mapsto z * z. prev \mapsto y * z. next \mapsto req * z. data \mapsto \_ *

17

dll_{\Lambda}(req, z, z, y) * locked(request_lock) *

18

sp..(ss + StackSize - 1) \mapsto .. \land sp = ss + 2 \cdot sizeof(Request*)

19

while (req != request_queue) {

20

\{reg \Vdash \exists x, y, z, u, v. \& request\_queue \mapsto z * z. prev \mapsto v * z. next \mapsto x * z. data \mapsto \_ *

21

\mathsf{dll}_{\Lambda}(x, z, req, y) * req. \mathtt{prev} \mapsto y * req. \mathtt{next} \mapsto u * req. \mathtt{data} \mapsto \_* \mathsf{dll}_{\Lambda}(u, req, z, v) *

22

locked(request_lock) * sp..(ss + StackSize - 1) \mapsto  \land

23

sp = ss + 2 \cdot sizeof(Request*)

24

if (stale_data(req->data)) remove_node(req);

25

\{req \Vdash \exists x, y, z, u, v. \& request\_queue \mapsto z * z. prev \mapsto v * z. next \mapsto x * z. data \mapsto \_ *

26

\mathsf{dll}_{\Lambda}(x,z,u,y) * req. \texttt{prev} \mapsto y * req. \texttt{next} \mapsto u * req. \texttt{data} \mapsto \_ * \mathsf{dll}_{\Lambda}(u,y,z,v) *

27

locked(request_lock) * sp..(ss + StackSize - 1) \mapsto  \land

28

29

sp = ss + 2 \cdot sizeof(Request*)

tmp = req;

30

req = req->next;

31

free(tmp);

32

\{req \Vdash \exists x, y, z, v. \& request\_queue \mapsto z * z. prev \mapsto v * z. next \mapsto x * z. data \mapsto \_ *

33

dll_{\Lambda}(x, z, req, y) * dll_{\Lambda}(req, y, z, v) * locked(request_lock) *

34

sp..(ss+StackSize-1) \mapsto \land sp = ss+2 \cdot sizeof(Request*)

35

}

36

\{req \Vdash \exists x, y, z. \& request\_queue \mapsto z * z. prev \mapsto y * z. next \mapsto x * z. data \mapsto \_ *

37

dll_{\Lambda}(x,z,z,y) * locked(request_lock) *

38

sp..(ss + StackSize - 1) \mapsto \land sp = ss + 2 \cdot sizeof(Request*)

30

unlock(request_lock);

40

\{req \Vdash sp.(ss + StackSize - 1) \mapsto \land sp = ss + 2 \cdot sizeof(Request*)\}

41

```

Fig. 4. An example system call part. The assertions are explained in Section 4

scheduler; thus, while verifying the OS, we have to prove that the two components do not corrupt each other's data structures.

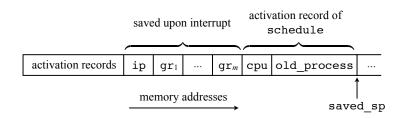

The schedule function. According to the semantics of our machine, when schedule starts executing, interrupts are disabled and the previous values of ip and the general-purpose registers are saved on the top of the stack. The scheduler uses the empty slots on the stack of the process it has preempted to store activation records of its procedures

Fig. 5. The invariant of the stack of a preempted process

and thus expects the kernel to leave enough of these. Intuitively, while a process is running, only this process has the right to access its stack, i.e., *owns* it. When the scheduler preempts the process, the right to access the empty slots on the stack (their *ownership*) is transferred to the scheduler. When the scheduler returns the control to this process, it transfers the ownership of the stack slots back. This is one example of ownership transfer we have to reason about.

The schedule function first calls load\_balance (line 32), which migrates processes between CPUs to balance the load; we describe it below. It then updates the timeslice of the currently running process, and if it becomes zero, proceeds to schedule another one (line 35); here we abstract from the particular way the timeslice is updated. The processes are scheduled in a round-robin fashion; thus, the function inserts the current process at the end of the local runqueue (line 38) and dequeues the process at the front of the runqueue, making it current (line 40).<sup>2</sup> The former is done using a library function insert\_node\_after, which inserts the node given as its second argument after the list node given as its first argument. The schedule function also refills the scheduling quantum of the process being descheduled (line 36). The runqueue manipulations are done with the corresponding lock held (lines 37 and 45). Note that in a realistic OS choosing a process to run would be more complicated, but still based on scheduler-private data structures protected by runqueue locks.

To save the state of the process being preempted, schedule copies sp into the saved\_sp field of the process descriptor (line 41). This field, together with the kernel\_stack of the process forms its saved state. The stack of a preempted process contains the activation records of functions called before the process was preempted, the label of the instruction to resume the process from and the values of general-purpose registers, saved upon the interrupt, as well as the activation record of schedule, as shown in Figure 5. This invariant holds for descriptors of all preempted processes.

The actual context switch is performed by the assignment to sp (line 42), which switches the current stack to another one satisfying the invariant in Figure 5. Since this changes the activation record of schedule, the function has to update the cpu variable (line 43), which lets it then retrieve and load the new value of ss (line 44). The iret command at the end of schedule (line 46) loads the values of the registers stored on the stack and enables interrupts, thus completing the context switch.

11

<sup>&</sup>lt;sup>2</sup> Actually, in Linux 2.6.11 the descriptor of the current process stays in the runqueue. We dequeue it because this simplifies the following formal treatment of the example.

# Alexey Gotsman and Hongseok Yang

The load\_balance function checks if the CPU given as its parameter is underloaded and, if it is the case, tries to migrate a process from another CPU to this one. The particular way the function performs the check and chooses the process is irrelevant for our purposes, and is thus abstracted by a random choice (line 50). To migrate a process, the function chooses a runqueue to steal a process from (line 51) and locks it together with the current runqueue in the order determined by the corresponding CPU identifiers, to avoid deadlocks (lines 52–54). The function then removes one process from the victim runqueue (line 57), if it is non-empty (line 55), and inserts the process into the runqueue of the CPU it runs on (line 58). Note that two concurrent scheduler invocations executing load\_balance on different CPUs may try to access the same runqueue. While verifying the scheduler, we have to ensure that they synchronise their accesses correctly. We also need to deal with the fact that, due to load\_balance, processes cannot be tied to a CPU statically.

The create function inserts the descriptor of a newly created process with the address given as its parameter into the runqueue of the current CPU. We pass the parameter via a register, as this simplifies the following treatment of the example. The descriptor must be initialised like that of a preempted process, and hence, its stack must satisfy the invariant in Figure 5. Upon a call to create, the ownership of the descriptor is transferred from the kernel to the scheduler. The create function must be called using icall, which disables interrupts; if interrupts were enabled, schedule could be called while create holds the lock for the current runqueue, resulting in a deadlock.

The fork function is formally not part of the scheduler. It illustrates how the rest of the kernel can use create to implement a common system call that creates a clone of the current process. This function allocates a new descriptor (line 76), copies the stack of the current process to it (line 77) and initialises the stack as expected by create (Figure 5). This amounts to discarding the topmost activation record of fork and pushing a fake activation record of schedule (line 78). We do not initialise the latter record, since schedule refreshes the values of the variables (line 43) when it receives control. Note that the values of registers in the initial state of the new process have been saved on the stack upon the call to fork. Since stack slots for return values are initialised with zeros, this is what fork in the child process will return; we return 1 in the parent process.

The need for modularity. We could try to verify the scheduler and the rest of the kernel (including, say, the system call in Figure 4) as a whole, modelling every CPU as a process in one of the existing program logics for concurrency (O'Hearn, 2007; Gotsman *et al.*, 2007; Feng *et al.*, 2007a; Vafeiadis & Parkinson, 2007; Dinsdale-Young *et al.*, 2010; Cohen *et al.*, 2010; Dinsdale-Young *et al.*, 2013). However, in this case our proofs would have to consider the possibility of the control flow going from any statement in a process to the schedule function, and from there to any other process. Thus, in reasoning about the system call implementation in Figure 4 we would end up having to reason explicitly about invariants and actions of both schedule and all other processes, making the reasoning non-modular and, most likely, intractable. In the rest of the paper we propose a logic that avoids this pitfall.

# 2.3 Approach

Before presenting our logic for preemptive kernels in detail, we give an informal overview of the reasoning principles behind it. The goal of the logic is to reason about the kernel and the scheduler separately. Following previous work on OS verification (Feng *et al.*, 2008b; Yang & Hawblitzel, 2010), our logic uses different proof systems for this purpose: the high-level one for the kernel and the low-level one for the scheduler.

Modular reasoning via memory partitioning. The first challenge we have to deal with in separating the reasoning about the kernel and the scheduler is the fact that they share the same address space. To this end, our logic partitions the memory into two disjoint parts. The memory cells in each of the parts are *owned* by the corresponding component, meaning that only this component can access them. In our running example, the runqueues from Figure 2 will belong to the scheduler, and the request queue from Figure 4 to the kernel. It is important to note that this partitioning does not exist in the semantics, but is enforced by proofs in the logic to enable modular reasoning about the system. Modular reasoning becomes possible because, while reasoning about one component, one does not have to consider the memory partition owned by the other, since it cannot influence the behaviour of the component. An important feature of our logic, required for handling schedulers from mainstream kernels, is that the memory partitioning is not required to be static: the logic permits ownership transfer of memory cells between the areas owned by the scheduler and the kernel according to an axiomatically defined interface. For example, in reasoning about the scheduler of Section 2.2, the logic permits the transfer of the descriptor for a new process from the kernel to the scheduler at a call to create; this descriptor then becomes part of a runqueue owned by the scheduler. Of course, assigning the ownership of parts of memory to OS components requires checking that a component does not access the memory it does not own. To this end, our logic implements a form of rely-guarantee reasoning between the scheduler and the kernel, where one component assumes that the other does not touch its memory partition and provides well-formed pieces of memory at ownership transfer points.

**Concurrent separation logic.** Our logic is based on concurrent separation logic (O'Hearn, 2007), which we recap in Section 4. In particular, this logic provides us with means for modular reasoning within a given component, i.e., either among concurrent OS processes or concurrent scheduler invocations on different CPUs. The choice of concurrent separation logic was guided by the convenience of presentation; see Section 8 for a discussion of how more advanced logics can be integrated. However, the use of a version of separation logic is crucial, because we inherently rely on the *frame property* validated by the logic: the memory that is not mentioned by assertions in a proof of a command is guaranteed not to be changed by it. As we have noted, while reasoning about a component, we consider only the memory partition belonging to it. Hence, by the frame property we automatically know that the component cannot modify the others. This makes it easy to carry out the above-mentioned rely-guarantee reasoning between the scheduler and the kernel: one does not need to state assumptions about one component not

10:8

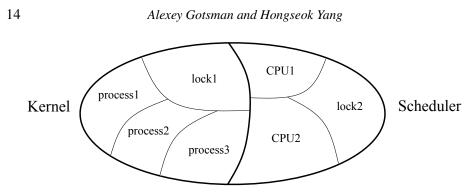

Fig. 6. The partitioning of the system state enforced by the logic. The memory is partitioned into two parts, owned by the scheduler and the kernel, respectively. The memory of each component is further partitioned into parts local to processes or scheduler invocations on a given CPU, and parts protected by locks.

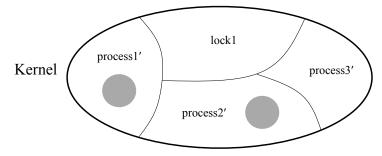

Fig. 7. The state of the abstract system with one virtual CPU per process. Process identifiers are primed to emphasise that the state of the process can be represented differently in the abstract and physical machines (cf. Figure 6). Dark regions illustrate the parts of process state that are tracked by a scheduler invocation running on a particular physical CPU.

modifying the memory of the other explicitly, as they will be automatically validated by the logic.

Concurrent separation logic lets us achieve modular reasoning within a given component by further partitioning the memory owned by it into disjoint process-local parts (one for each process or scheduler invocation on a given CPU) and protected parts (one for each free lock). A process-local part can only be accessed by the corresponding process or scheduler invocation, and a lock-protected part only when the process holds the lock. The resulting partitioning of the system state is illustrated in Figure 6. The frame property guarantees that a process cannot access the partition of the heap belonging to another one. To reason modularly about parts of the state protected by locks, the logic associates with every lock an assertion—its *lock invariant*—that describes the part of the state it protects. Lock invariants restrict how processes can change the protected state, and hence, allow reasoning about them in isolation. For example, in the program from Figure 4, the invariant of request\_lock can state that it protects the request\_queue variable and the doublylinked list it identifies.

Scheduler-agnostic verification of kernel code. The high-level proof system (Section 5.2) reasons about preemptable code assuming an abstract machine where every

process has its own virtual CPU with a dedicated set of registers. It relies on the partitioned view of memory described above to hide the state of the scheduler, with all the remaining state split among processes and locks accessible to them, as illustrated in Figure 7. We have primed process identifiers in the figure to emphasise that the state of the process can be represented differently in the abstract and physical machines: for example, if a process is not running, the values of its local registers can be stored in scheduler-private data structures, rather than in CPU registers.

Apart from hiding the state of the scheduler, the high-level system also hides the complex manipulation of the control flow performed by its context-switch code: the proof system assumes that the control moves from one point in the process code to the next without changing its state, ignoring the possibility of the context-switch code getting executed upon an interrupt. This is expressed by handling sequential composition in the proof system essentially using the standard rule (1) from Hoare logic. Explicit calls to the scheduler are treated as if they were executed atomically.

Technically, the proof system is a straightforward adaptation of concurrent separation logic, which is augmented with proof rules axiomatising the effect of scheduler routines explicitly called by processes. The novelty here is that we can use such a scheduler-agnostic logic in this context at all. This is made possible by verifying the scheduler implementation using the low-level proof system (Section 5.3).

**Proving schedulers correct.** Intuitively, a correct scheduler provides an illusion of the above-mentioned abstract machine with one CPU per process, but what formal obligations does this entail? First, a process should not notice any effects of being preempted and then scheduled again: whenever the scheduler sets up a process to run on a CPU, it has to restore the state of the CPU registers to the one the process had last time it was preempted. The low-level proof system ensures this by recording these values in a special predicate Process, which can be viewed as an assertion about the continuation of a process describing the states from which it can be safely resumed.

In more detail, when a process is preempted and the control is given to the context-switch routine of the scheduler (schedule in the example from Section 2.2), a Process predicate recording the current values of the CPU registers appears in its precondition. When the context-switch routine terminates and the control is given to the process it resumes, the proof system requires the postcondition of the routine to exhibit a Process predicate with register values equal to the ones loaded onto the CPU. Roughly speaking, we thus require the following judgement to hold of the context-switch routine schedule:

$$\{\exists \vec{r}. \operatorname{Process}(\vec{r}) \land \vec{r} = \vec{r}...\} \text{ schedule } \{\exists \vec{r'}. \operatorname{Process}(\vec{r'}) \land \vec{r} = \vec{r'}...\},$$

(2)

where  $\vec{r}$  is the vector of CPU register names. The Process predicate in the postcondition may correspond to a different process than the predicate in the precondition. For example, when the scheduler from Section 2.2 preempts a process and links its descriptor into a runqueue, assertions about the runqueue in the proof system can record the corresponding Process predicate with register values equal to the ones stored in the descriptor. This predicate can then be used to establish the postcondition of the context-switch routine when it decides to schedule the process again.

# Alexey Gotsman and Hongseok Yang

In the case of multiprocessors, ensuring that the scheduler preserves the state of a preempted process is not enough for it to be correct. The scheduler should also be prevented from duplicating processes at will: it would be incorrect to preempt one process and then schedule two copies of it on two CPUs at the same time. To check that this does not happen, the proof system interprets a Process predicate as not merely recording a process state, but serving as an exclusive permission for the scheduler invocation owning it to schedule the corresponding process. Technically, it treats Process predicates affinely, prohibiting their duplication. Judgement (2) is then interpreted as stating that the scheduler gets the ownership of a Process predicate when it preempts a process and gives it up when scheduling that process again. This ensures that, at any time, only a scheduler invocation on a single CPU can own a Process predicate for a given process and, hence, can schedule it. In terms of Figure 6, a Process predicate can only belong to one partition in the scheduler owned memory at a time.

We note that the problem of interdependence between the correctness of the scheduler and the rest of the kernel that we address in this paper also arises in preemptive *uniprocessor* kernels. The Process predicate also allows us to verify schedulers on uniprocessors; however, its affine treatment described above is not relevant in this case.

Assertions of the low-level proof system can be thought of as relating the states of the concrete machine and the abstract one the scheduler is supposed to implement. An important feature of our logic is that this relation is *local*, in the sense that it does not describe the whole state of the two machines. Namely, since we use concurrent separation logic to reason about concurrent execution of scheduler invocations on different CPUs, an assertion in the low-level proof system describes only the state owned by a scheduler invocation on a particular CPU (e.g., the region marked CPU1 in Figure 6). Similarly, the Process predicates describe only the registers of the processes a scheduler invocation has permission to schedule (shown by the dark regions in Figure 7), but not the memory they own. Since the assertions about the scheduler cannot talk about the scheduler cannot corrupt it.

**Soundness.** We establish the soundness of our logic using an approach atypical for the kind of setting we consider. Since a scheduler is supposed to provide an illusion of an abstract machine with one CPU per process, to formalise its correctness, we could define an operational semantics of such an abstract machine and prove that it reproduces any behaviour of the concrete machine with the scheduler, thus establishing a *refinement* between the two machines. However, for realistic OS schedulers defining a semantics for the abstract machine that a scheduler implements is difficult. This is because, in reasoning about mainstream operating systems, the state transferred between the scheduler and the kernel can be described by complicated assertions; in such cases, defining ownership transfer operationally is difficult (we discuss this further in Section 8).

To resolve this problem with stating soundness, we do not define the semantics of the abstract machine operationally; instead, we describe its behaviour only by the high-level proof system, thus giving it an axiomatic semantics. As expected, the low-level proof system is used to reason about the correspondence between the concrete and the abstract machines, with its assertions relating their states. However, proofs in neither of the two

systems are interpreted with respect to any semantics alone: our soundness statement (Section 8) interprets a proof of the kernel in the high-level system and a proof of the scheduler in the low-level one together with respect to the semantics of the concrete machine. Thus, instead of relating sets of executions of the two machines, like in the classical refinement, the soundness statement relates logical statements about the abstract machine (given by high-level proofs) to logical statements about the concrete one (given by a constraint on concrete states). Note that in this case the soundness statement for the logic does not yield a semantic statement of correctness for the scheduler being considered in isolation. Rather, its correctness is established indirectly by the fact that reasoning in the high-level proof system, which assumes the abstract one-CPU-per-process machine, is sound with respect to the concrete machine.

To formulate the soundness statement in the above way, we need to construct a global property about the whole system state shown in Figure 6 from local assertions about its components, corresponding to partitions in Figure 6. This does not just boil down to combining the assertions about the partitions using the separating conjunction, since the high-level and low-level proof systems work on different levels of abstraction. In particular, when conjoining assertions about the scheduler and the kernel, we need to make sure that the view of the parts of kernel state in the assertions about the scheduler (dark regions in Figure 7) is consistent with those about the kernel. This requires a delicate construction, combining relational composition and separating conjunction. Similar constructions can potentially be used for justifying other program logics working on several levels of abstraction at the same time.

#### **3** Machine semantics

In this section, we give a formal semantics to the example machine informally presented in Section 2.1.

#### 3.1 Storage model

Figure 8 gives a model for the set of configurations Config that can arise during an execution of the machine. A machine configuration is a triple with the components describing the values of registers of the CPUs in the machine (its *global context*), the state of the heap and the set of locks taken by some CPU (the *lockset* of the machine). Note that we allow the global context or the heap to be a partial function. However, the corresponding configurations are not encountered in the semantics we define in this section. They come in handy in Sections 5 and 8 to give a semantics to the assertion language and express the soundness of our logic.

In this paper, we use the following notation for partial functions: f[x : y] is the function that has the same value as f everywhere, except for x, where it has the value y; [] is a nowhere-defined function; f

rightarrow g is the union of the disjoint partial functions f and g.

## 3.2 Programming language

We consider a low-level language where programs are represented by structures similar to control-flow graphs. The programs are constructed from primitive commands c, whose

Alexey Gotsman and Hongseok Yang

| $k \in CPUid$       | $= \{1, \dots, \texttt{NCPUS}\}$       | $\mathtt{r}~\in~Reg$ | $= \ \{\texttt{ip},\texttt{if},\texttt{ss},\texttt{sp},\texttt{gr}_1,\ldots,\texttt{gr}_m\}$ |

|---------------------|----------------------------------------|----------------------|----------------------------------------------------------------------------------------------|

| $r \in Context$     | $= \ Reg \to Val$                      | $R \in GContext$     | i = CPUid $ ightarrow$ Context                                                               |

| $\ell \ \in \ Lock$ | $= \{\ell_1, \ell_2, \ldots, \ell_n\}$ | $L \in Lockset$      | $= \mathscr{P}(Lock)$                                                                        |

| $h \in Heap$        | $= Loc \rightharpoonup Val$            | $(R,h,L) \in Config$ | $= \ GContext \times Heap \times Lockset$                                                    |

Fig. 8. The set of machine configurations Config. We assume sets Loc of valid memory addresses and Val of values such that Loc  $\subseteq$  Val.

$\operatorname{Reg} - \{ ip, if \}$ r  $\in$ l  $\in$ Lock  $\in$  Label =  $\mathbb{N}$ 1 ::= r | 0 | 1 | 2 | ... | e + e | e - eе b  $::= e = e \mid e < e \mid b \land b \mid b \lor b \mid \neg b$  $::= \text{ skip } | \mathbf{r} := e | \mathbf{r} := [e] | [e] := e | \text{ assume}(b) | \text{ lock}(\ell) | \text{ unlock}(\ell)$ с savecpuid(e) | call(l) | icall(l) | ret | iret

#### Fig. 9. Primitive commands

syntax we define in Figure 9. In addition to the primitive commands listed in Section 2, we have the following ones: skip and r := e have the standard meaning; r := [e] reads the contents of a heap cell e and assigns the value read to r; [e] := e' updates the contents of cell e by e'; assume(b) acts as a filter on the state space of programs, choosing states satisfying b. The assume command is used to treat branches in conditionals and loops uniformly with the other primitive commands, as we explain below. We write PComm for the set of primitive commands. Note that primitive commands cannot access the ip register directly. Also, only icall and iret can affect the if register, a restriction that we lift in Section 7.

Commands *C* are partial maps from Label to  $PComm \times \mathscr{P}(Label)$ . Intuitively, if C(l) = (c,X), then *c* is labelled by *l* in *C* and can be followed by any command with a label in *X*. In this case we let comm(C,l) = c and next(C,l) = X. We denote the domain of *C* by labels(*C*) and the set of all commands by Comm.

The language constructs used in the example scheduler of Section 2, such as sequential composition, loops and conditionals, can be expressed as commands in a standard way, with conditions translated using assume. We illustrate this in Figure 10, where we represent the mapping C by a graph, with nodes annotated by labels and primitive commands and edges defining the next function.

#### 3.3 Operational semantics

We now give a standard operational semantics to our programming language. We interpret primitive commands *c* using a transition relation  $\sim_c$  of the following type:

$$State = Context \times Heap \times Lockset;$$

(3)

$$\sim_{c} \subseteq (CPUid \times State \times Label \times Label) \times ((State \times Label) \cup \{\top\}).$$

The input (k, (r, h, L), l, l') to  $\sim_c$  consists of the following components:

Fig. 10. Representing sequential composition and conditionals in our low-level language

- $k \in CPUid$  is the identifier of the CPU executing the command.

- (r,h,L) is the configuration of the system projected to this CPU, which we call a *state*. It includes the context of the CPU and the information about the shared resources—the heap and locks.

- $l \in Label$  is the label of the command c.

- $l' \in Label$  is the label of a primitive command following c in the program.

Given this input, the transition relation  $\rightsquigarrow_c$  for *c* computes the next state of the CPU after running *c*, together with the label of the primitive command to run next. The former may be a special  $\top$  state signalling a machine crash. The latter may be different from l' when *c* is a call or a return.

The relation  $\rightsquigarrow_c$  is defined in Figure 11. In the figure and in the rest of the paper, we write \_ for an expression whose value is irrelevant and implicitly existentially quantified and  $\vec{gr}$  for the vector of general-purpose registers. The relation follows the informal meaning of primitive commands given in Sections 2.1 and 3.2. We have omitted standard definitions for skip and most of assignments; see (Reynolds, 2002). We have also omitted them for icall and iret: the definitions are the same as for call and ret, but additionally modify if. Note that  $\rightsquigarrow_c$  may yield no post-state for a given pre-state. Unlike a transition to the  $\top$  state, this represents the command getting stuck. For example, according to Figure 11, acquiring the same lock twice leads to a deadlock, and releasing a lock that is not held crashes the system.

The program our machine executes is given by a command *C* that includes a primitive command labelled schedule, serving as the entry point of the interrupt handler. For such a command *C*, we give its meaning using a small-step operational semantics, formalised by the transition relation  $\rightarrow_C \subseteq$  Config  $\times$  (Config  $\cup$  { $\top$ }) in Figure 12. The first rule in the figure describes a normal execution, where the value *l* of the ip register of CPU *k* is used to choose the primitive command *c* to run. After choosing *c*, the machine nondeterministically picks a label  $l' \in next(C, l)$  identifying the command to follow *c*, runs *c* according to the semantics  $\rightarrow_c$ , and uses the result of this run to update the registers of CPU *k* and the heap and the lockset of the machine. For example, when a CPU executes the program in

19

# Alexey Gotsman and Hongseok Yang

| (k, (r, h[[[e]]r : u], L), l, l')                                                                                                                                | $\rightsquigarrow_{\mathbf{r}:=[e]}$    | $((r[\texttt{r}:u],h[[\![e]]\!]r:u],L),l')$                  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------|--|--|

| (k, (r, h, L), l, l')                                                                                                                                            | $\rightsquigarrow_{\texttt{assume}(b)}$ | $((r,h,L),l'), \text{ if } \llbracket b \rrbracket r = true$ |  |  |

| (k,(r,h,L),l,l')                                                                                                                                                 | $\not \sim_{\texttt{assume}(b)}$        | if $[\![b]\!]r = false$                                      |  |  |

| (k,(r,h,L),l,l')                                                                                                                                                 | $\leadsto_{\texttt{lock}(\ell)}$        | $((r,h,L\cup\{\ell\}),l'), \text{ if } \ell \not\in L$       |  |  |

| (k,(r,h,L),l,l')                                                                                                                                                 | $\not\sim$ lock $(\ell)$                | $\text{if}\ \ell\in L$                                       |  |  |

| (k,(r,h,L),l,l')                                                                                                                                                 | $\sim_{\texttt{unlock}(\ell)}$          | $((r,h,L-\{\ell\}),l'),$ if $\ell\in L$                      |  |  |

| $(k,(r,h[\llbracket e \rrbracket r: \_],L),l,l')$                                                                                                                | $\leadsto_{\texttt{savecpuid}(e)}$      | $((r,h[\llbracket e \rrbracket r:k],L),l')$                  |  |  |

| $(k,(r,h[r(\mathtt{sp})(r(\mathtt{sp})+m):\_],L),l,l')$                                                                                                          | $\sim_{call}(l'')$                      |                                                              |  |  |

| $((r[\mathtt{sp}:r(\mathtt{sp})+m+1],h[r(\mathtt{sp}):l',(r(\mathtt{sp})+1)(r(\mathtt{sp})+m):r(\vec{\mathtt{gr}})],L),l'')$                                     |                                         |                                                              |  |  |

| $(k,(r,h[r(\mathtt{sp})-m-1:l'',(r(\mathtt{sp})-m)(r(\mathtt{sp})-1):\vec{g}],L),l,l') \leadsto_{\mathtt{ret}}$                                                  |                                         |                                                              |  |  |

| $((r[\mathtt{sp}:r(\mathtt{sp})-m-1,\vec{\mathtt{gr}}:\vec{\mathtt{g}}],h[r(\mathtt{sp})-m-1:l'',(r(\mathtt{sp})-m)(r(\mathtt{sp})-1):\vec{\mathtt{g}}],L),l'')$ |                                         |                                                              |  |  |

| (k,(r,h,L),l,l')                                                                                                                                                 | $\sim_c$                                | $\top$ , otherwise                                           |  |  |

Fig. 11. Semantics of primitive commands. The notation  $\sim_c \top$  indicates that the command *c* crashes, and  $\gamma_c$  that it does not crash, but gets stuck. The function  $[\cdot]r$  evaluates expressions with respect to the context *r*.

$$\begin{split} \frac{r(\texttt{ip}) = l \in \texttt{labels}(C) \qquad l' \in \texttt{next}(C,l) \qquad (k,(r,h,L),l,l') \rightsquigarrow_{\texttt{comm}(C,l)} ((r',h',L'),l'')}{(R[k:r],h,L) \rightarrow_C (R[k:r'[\texttt{ip}:l'']],h',L')} \\ \frac{r(\texttt{ip}) = l \in \texttt{labels}(C) \qquad r(\texttt{if}) = 1 \qquad (k,(r,h,L),l,l) \rightsquigarrow_{\texttt{icall}(\texttt{schedule})} ((r',h',L'),l'')}{(R[k:r],h,L) \rightarrow_C (R[k:r'[\texttt{ip}:l'']],h',L')} \\ \frac{r(\texttt{ip}) = l \in \texttt{labels}(C) \qquad l' \in \texttt{next}(C,l) \qquad (k,(r,h,L),l,l') \rightsquigarrow_{\texttt{comm}(C,l)} \top}{(R[k:r],h,L) \rightarrow_C \top} \\ \frac{r(\texttt{ip}) \notin \texttt{labels}(C)}{(R[k:r],h,L) \rightarrow_C \top} \\ \frac{r(\texttt{if}) = 1 \qquad \{r(\texttt{sp}), \dots, r(\texttt{sp}) + m\} \not\subseteq \texttt{dom}(h)}{(R[k:r],h,L) \rightarrow_C \top} \end{split}$$

Fig. 12. Operational semantics of the machine

Figure 10 from label 0, both labels 1 and 2 following it will be explored; however, only the branch where the assume condition evaluates to true will proceed further.

The second rule in Figure 12 concerns interrupts. Upon an interrupt, the interrupt handler label schedule is loaded into ip, and the label of the command to execute after the handler returns is pushed onto the stack together with the values of the general-purpose registers. The remaining rules deal with crashes arising from erroneous execution of primitive commands, undefined command labels and a stack overflow upon an interrupt.

#### **4** Baseline concurrency logic

We start by presenting the variation of concurrent separation logic on which our logic for verifying preemptive kernels is based (Section 5). The logic we present in this section assumes that interrupts are disabled on all CPUs. Thus, we assume that all if registers

are initially set to zero and only consider programs that do not use icall, iret and savecpuid commands. One can thus think of a single process having been pinned to every CPU, so that we do not have to consider scheduling. Our logic for preemptive kernels in Section 5 lifts this restriction.

#### 4.1 Assertion language

Mathematically, assertions denote sets of states as defined by (3). However, they describe properties of a single process, rather than the whole machine. Hence, unlike in Section 3.3, here a heap can be a partial function, with its domain defining the part of the heap owned by the process. Similarly, a lockset is now meant to contain only the set of locks that the process has permission to release.

We use a minor extension of the assertion language of separation logic (Reynolds, 2002), whose syntax and semantics are defined in Figure 13. We denote the set of assertions by Assert<sub>H</sub>. We assume disjoint sets NVar and CVar containing logical variables for values and contexts, respectively. The latter is needed for the extension of the current logic to reasoning about preemptive kernels (Section 5). A context *G* is either a logical variable or a finite map from register labels **r** to expressions. Note that we use **r** to range over register names in context expressions, but **r** elsewhere in assertions and in programs. Expressions *E* and Booleans *B* are similar to those in programs, except that they allow logical variables to appear and include the lookup  $G(\mathbf{r})$  of the value of the register **r** in the context *G*. Let a logical variable environment  $\eta$  be a mapping from NVar  $\cup$  CVar to Val  $\cup$  Context that respects the types of variables. Assertions denote sets of states from State as defined by the satisfaction relation  $\models_{\eta}$  in Figure 13. For an environment  $\eta$  and an assertion *P*, we denote the set of states satisfying *P* by  $[\![P]\!]_{\eta}$ .

The assertions in the first line of the definition of P are connectives from the firstorder logic with the standard semantics. We can define the missing connectives from the given ones. The assertions in the second line up to dll<sub>A</sub> are standard assertions of separation logic (Reynolds, 2002). Informally, emp describes the empty heap, and  $E \mapsto E'$ the heap with only one cell at the address E containing E'. The assertion  $E..E' \mapsto \Sigma$  is the generalisation of the latter to several consecutive cells at the addresses from E to E'inclusive containing the sequence of values  $\Sigma$ . For a value u of a C type t taking several cells, we shorten  $E..(E + sizeof(t) - 1) \mapsto u$  to just  $E \mapsto u$ . For a field f of a C structure, we use  $E.f \mapsto E'$  as a shorthand for  $(E + off) \mapsto E'$ , where off is the offset of f in the structure. The separating conjunction  $P_1 * P_2$  talks about the splitting of the local state, which consists of the heap and the lockset of the process. It says that a pair (h, L) can be split into two disjoint parts, such that one part  $(h_1, L_1)$  satisfies  $P_1$  and the other  $(h_2, L_2)$ satisfies  $P_2$ .

The assertion  $dll_{\Lambda}(E_h, E_p, E_n, E_t)$  is an inductive predicate describing a segment of a doubly-linked list (Figure 14). We included it to describe the runqueues of the scheduler in our example; predicates for other data structures can be added straightforwardly (Reynolds, 2002). The predicate assumes a C structure definition with fields prev and next. Here  $E_h$  is the address of the head of the list,  $E_t$  the address of its tail,  $E_p$  the pointer in the prev field of the head node, and  $E_n$  the pointer in the next field of the tail node. The  $\Lambda$  parameter is a formula with one free logical variable describing the shape of each node in the list,

# Alexey Gotsman and Hongseok Yang

excluding the prev and next fields; the logical variable defines the address of the node. For instance, the request queue from Figure 4 can be described by the following assertion:

$\exists x, y, z. \&$ request\_queue  $\mapsto z * z.$  prev  $\mapsto y * z.$  next  $\mapsto x * z.$  data  $\mapsto -*$  dll<sub>A</sub>(x, z, z, y), (4)

where  $\Lambda(x) = x.\mathtt{data} \mapsto \_$ .

Finally, the assertion locked( $\ell$ ) is specific to reasoning about concurrent programs and denotes states with an empty local heap and the lockset consisting of  $\ell$ , i.e., it denotes a permission to release the lock  $\ell$ . Note that locked( $\ell$ ) \* locked( $\ell$ ) is inconsistent: acquiring the same lock twice leads to a deadlock.

In the following, we write  $var \Vdash P$  for a local C variable or procedure parameter var instead of  $\exists var. (sp - var_off) \mapsto var * P$ , where  $var_off$  is the offset of var with respect to the top of the stack in the activation record of the function where it is declared (note that here var is a program variable, whereas var is a logical one). Thus, the assertion at line 13 of Figure 4 states that the local state of a process executing the system call consists of the local variables req and tmp, stored on its stack, the free part of the stack, the doubly-linked list request\_queue and a permission to release request\_lock.

To summarise, our assertion language extends that of concurrent separation logic with expressions to denote contexts and locked assertions to keep track of permissions to release locks.

# 4.2 Proof system

The proof system for the baseline logic is obtained by adapting concurrent separation logic to our low-level language. The judgements of the proof system are of the form  $I, \Delta \vdash C$ . Here C specifies the code executed by processes on all CPUs; note that even though C is the same for all of them, the processes can still execute different programs if they start from different program points in C. We explain I below. The parameter  $\Delta$ : Label  $\rightarrow$  Assert<sub>H</sub> in our judgement specifies local states of a process given the program point it is at; these states correspond to process partitions in Figure 7. It thus induces pre- and post-conditions for all primitive commands in C. The top-level rule PROG of the proof system requires us to prove  $I, \Delta \succ_{l'} \{\Delta(l)\} c \{\Delta(l')\}$  for every primitive command c in C and the label l' of a command following c. This informally means that, if c is run from an initial state satisfying  $\Delta(l)$ , then it accesses only the memory specified by  $\Delta(l)$  and either terminates normally and ends up in a state satisfying  $\Delta(l')$ , or jumps to a label l'' whose assertion  $\Delta(l'')$ holds in the current state. The proof rules for the above kind of judgements are also given in Figure 15. They include the standard separation logic axioms for primitive commands, such as ASSUME and STORE; see (Reynolds, 2002) for the others. Note that PROG treats sequential composition, represented by  $\Delta$  as illustrated in Figure 10, in the same way as the classical proof rule (1).

The fact that  $I, \Delta \triangleright_{l'} \{\Delta(l)\} c \{\Delta(l')\}$  guarantees that *c* accesses only the memory specified by  $\Delta(l)$  validates the frame property (Section 2.3): a process will not step out of the boundaries of its partition in Figure 7. This also allows us to include the FRAME rule of separation logic, which states that executing a command in a bigger local state does not change its behaviour. The rule is useful to restrict the reasoning about primitive commands to the memory they actually access. The rules CONSEQ, DISJ and EXISTS are

| x, y | $\in$ | NVar                                                                                                         |

|------|-------|--------------------------------------------------------------------------------------------------------------|

| γ    | $\in$ | CVar                                                                                                         |

| r    | $\in$ | ${\sf Reg}-\{{\tt ip}, {\tt if}\}$                                                                           |

| r    | $\in$ | $\{\mathbf{ip}, \mathbf{if}, \mathbf{ss}, \mathbf{sp}, \mathbf{gr}_1, \dots, \mathbf{gr}_m\}$                |

| Ε    | ::=   | $x \mid \mathbf{r} \mid 0 \mid 1 \mid \mid E + E \mid E - E \mid G(\mathbf{r})$                              |

| G    | ::=   | $\gamma \mid [\mathbf{ip}: E, \mathbf{if}: E, \mathbf{ss}: E, \mathbf{sp}: E, \mathbf{gr}: \vec{E}]$         |

| Σ    | ::=   | $oldsymbol{arepsilon} \mid E \mid \Sigma \Sigma$                                                             |

| В    | ::=   | $E = E \mid \Sigma = \Sigma \mid G = G \mid E \leq E \mid B \land B \mid B \lor B \mid \neg B$               |

| Р    | ::=   | $B \mid true \mid P \land P \mid \neg P \mid \exists x. P \mid \exists \gamma. P$                            |

|      |       | $emp \mid E \mapsto E \mid EE \mapsto \Sigma \mid P \ast P \mid dll_{\Lambda}(E, E, E, E) \mid locked(\ell)$ |

| $(r,h,L)\models_{\eta} B$                             | iff | $\llbracket B \rrbracket_{\eta} r = true$                                                                                 |

|-------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------|

| $(r,h,L)\models_{\eta} P_1 \wedge P_2$                | iff | $(r,h,L)\models_{\eta} P_1$ and $(r,h,L)\models_{\eta} P_2$                                                               |

| $(\mathit{r},\mathit{h},\mathit{L})\models_{\eta}emp$ | iff | $h = []$ and $L = \emptyset$                                                                                              |

| $(r,h,L)\models_{\eta} E_0\mapsto E_1$                | iff | $h = [\llbracket E_0 \rrbracket_\eta r : \llbracket E_1 \rrbracket_\eta r]$ and $L = \emptyset$                           |

| $(r,h,L)\models_{\eta} E_0E_1\mapsto \Sigma$          | iff | $\exists j \ge 0. \exists u_1, \dots, u_j \in Val. \ L = \emptyset, \ j = [\![E_1]\!]_\eta r - [\![E_0]\!]_\eta r + 1,$   |

|                                                       |     | $u_1 u_2 \dots u_j = [\![\Sigma]\!]_{\eta} r$ and $h = [\![\![E_0]\!]_{\eta} r : u_1, \dots, [\![E_1]\!]_{\eta} r : u_j]$ |

| $(r,h,L)\models_{\eta}locked(\ell)$                   | iff | $h = []$ and $L = \{\ell\}$                                                                                               |

| $(r,h,L)\models_{\eta} P_1*P_2$                       | iff | $\exists h_1, h_2, L_1, L_2. \ h = h_1 \uplus h_2, \ L = L_1 \uplus L_2,$                                                 |

|                                                       |     | $(r,h_1,L_1)\models_{\eta} P_1$ and $(r,h_2,L_2)\models_{\eta} P_2$                                                       |

Predicate  $dll_{\Lambda}$  is the least one satisfying the equivalence below:

$$dll_{\Lambda}(E_h, E_p, E_n, E_t) \iff \exists x. (E_h = E_n \land E_p = E_t \land emp) \lor \\ E_h \cdot prev \mapsto E_p * E_h \cdot next \mapsto x * \Lambda(E_h) * dll_{\Lambda}(x, E_h, E_n, E_t)$$

Fig. 13. Syntax and semantics of assertions of the baseline logic. We have omitted the standard clauses for most of the first-order connectives. The function  $[\![\cdot]\!]_{\eta}r$  evaluates expressions with respect to the context *r* and the logical variable environment  $\eta$ .

Fig. 14. An illustration of the  $dll_{\Lambda}(E_h, E_p, E_n, E_t)$  predicate

standard rules of Hoare logic. To keep the logic sound we have to forbid applying EXISTS and FRAME to calls or returns.

The LOCK and UNLOCK axioms are inherited from concurrent separation logic and provide tools for modular reasoning about concurrent processes. They use the mapping  $I : Lock \rightarrow Assert_H$ , which specifies the invariants of locks that can be used in C (see Section 2.3). An example of a lock invariant is the assertion (4), which states that the lock request\_lock from Figure 4 protects a non-empty cyclic doubly-linked list of Request nodes with the head node at address request\_queue. We do not allow lock invariants to contain registers or free occurrences of logical variables and require them to have

#### Alexey Gotsman and Hongseok Yang

$$\frac{\forall l \in \mathsf{labels}(C). \forall l' \in \mathsf{next}(C,l). (I, \Delta \rhd_{l'} \{\Delta(l)\} \operatorname{comm}(C,l) \{\Delta(l')\})}{I, \Delta \vdash C} \operatorname{Prog} \operatorname{Assume} (D, \{\Delta \vdash Q\} \operatorname{Conseq} (D, \{D, \{\Delta \vdash Q\} \operatorname{Conseq} (D, \{A \vdash Q}$$

Fig. 15. Proof system of the baseline logic. Here mod(c) is the set of registers modified by c, and free(F) is the set of registers appearing in F.

an empty lockset:  $\forall \ell, \eta, (r, h, L) \in [[I(\ell)]]_{\eta} \cdot L = \emptyset$ . The latter does not allow us to prove programs where a lock is released by a CPU other than the one that acquired it, which our machine semantics allows. We put this restriction to simplify the explanation of soundness in Section 8. We consider a version of concurrent separation logic where lock invariants are allowed to be imprecise (O'Hearn, 2007) at the expense of excluding the conjunction rule from the proof system (Gotsman *et al.*, 2011).

The LOCK axiom says that, upon acquiring a lock, the process gets the ownership of its invariant and a permission to release it. In terms of Figure 7, we can think of the corresponding lock partition becoming part of the process-local one, allowing the process to modify it at will. According to UNLOCK, before releasing the lock, the process must have the corresponding permission and must re-establish the lock invariant. When the lock is released, the process gives up the ownership of the permission and the invariant. In terms of Figure 7, the lock partition gets split off the process-local one.